# **Custom Performance with ASIC Effort**

# **Greater Designer Control**

### HIGH-PERFORMANCE DATAPATHS

# **HOW DPC SOLVES THE** POWER/PERFORMANCE PROBLEM:

- 1 Import design data using schematics or Verilog.

- 2. Creates custom-like bit-slice placement which reduces congestion and improves routing.

- Performs postplacement timing analysis.

- 4. Computes critical paths and provides timing information at each node.

- 5. Auto-sizes gates based on your constraints (optimizing for timing and power, or power alone).

- Modify your design and see the new results very quickly. Iterations are done in minutes - DPC computes 100,000 gates per minute.

- Checks for "hot spots" with congestion analysis.

- 8. Outputs a DEF placement file for your existing P&R flow.

- **Verifies timing post**route, and shows results graphically.

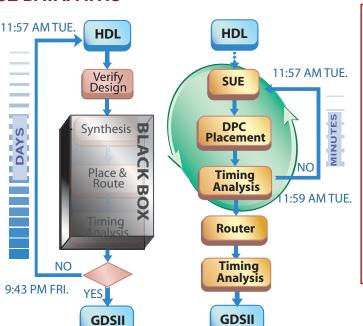

Standard **ASIC** flow is a "black box" providing little information. Iterations take days/weeks.

**DPC flow** provides timing feedback early in the design process. **Iterations** take seconds/ minutes.

**Verilog or Schematics** to enter design information. nand3 (q, s, qbar), nand4 (qbar, r, q); CRITICAL PATH ANALYSIS Select Critical Path: : 1591ps to out[3] (net\_6[2] -> out[3]) **DPC** computes ns to out[7] (net\_6[2] -> out[7]) placement, route, and

Critical paths are displayed on the schematic and placement views.

timing information.

Display CP Display All

# **Control Your Gate Sizing**

DPC automatically sizes the gates in your datapath, using a production-proven algorithm to select optimal sizes for speed, power or both. Using the "power down" option, Auto-Sizer will only down-size gates in order to minimize power required. At your option, you can also manually resize gates.

### Timing Information and Critical-Path Analysis

DPC provides immediate timing feedback for placement and gate sizing. Multiple what-if experiments can be performed in seconds. Using a graphical display that back annotates timing to the schematic and placement file, you can easily identify timing problems and

rapidly iterate through solutions. DPC is so fast it can place. route, and time a 100,000 gate datapath in one minute.

# **Design Inputs**

**Manage Your Design with**

SUE combines schematic

control of Verilog blocks, timing

and documentation. SUE is useful

from an architectural level to plan

models, standard cell libraries

your design, and manage the

capture and verification with

DPC reads your Verilog and produces a schematic. For designers who don't use schematics, there is a "VerilogOnly" option. Once you are meeting your timing and power goals, you can use the built-in congestion analyzer to check for hot spots. Due to the regular bitslice placement and congestion check, DPC blocks usually route correctly on the first pass.

A DEF placement file and the Verilog netlist is sent to your router.

# **DPC Incorporates SUE SoC Design Manager** SOC DESIGN MANAGER

SUE

**Everything Needed to Manage Today's SoC Design Flow**

#### **BEHAVIORAL STRUCTURAL** TIMING/SIM **SCHEMATICS DOCUMENTATION VERILOG VERILOG TOOLS**

• The Framework for All Design Capture, Simulation, Timing and Data Management

**Control Your Placement**

DPC gives the designer

datapath. You control relative

placement for specific gates.

complete control of the

placement of gates, and

you can designate exact

- Manage Circuits, Verilog, **Documentation and Version Control**

- Fast and Effective **Schematic Capture Tool**

- Supports Industry Standard File Formats

design process.

» Fully hierarchical, SUE can drill down to gate-level or transistorlevel detail of any block.

of your design.

» Provides an architectural overview

- » Structural Verilog is imported and automatically arranged as a schematic.

- » Enter your designs quickly with the simple graphical user interface.

## **DPC Features**

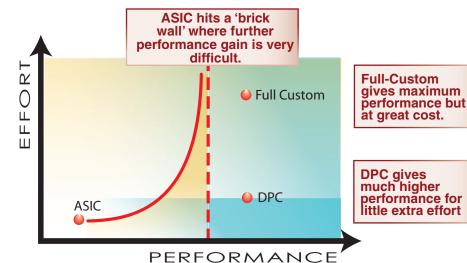

- Up to 300% Faster Datapath Performance, 40% Lower Power, 40% Less Area.

- Custom performance with **ASIC** effort.

- Quickly builds custom-like datapaths using all existing standard cell libraries.

- DPC includes its own timing analyzer, or you can use PrimeTime®.

- Fast processes 100,000 gates per minute.

- Writes DEF placement information and a Verilog netlist for integration with routers.

- Available on LINUX.

#### **SUE Features:**

- » Draw, view, and edit schematics, icons, graphics, and text.

- » Automatically:

- » Attach Verilog models and documentation to schematics.

- » Generate Verilog from schematic symbols and vice versa.

- » Generate layout when used with **MAX-LS Layout System.**

- » Highlight nets and cross-probe between layout and schematic.

- » Maintain multiple views (behavioral, RTL, structural) of schematics.

- » Interactive cross-probing during simulation on schematic or waveform tool.

- » Includes waveform viewer.

- » Reads/writes OVI compliant Verilog files.

- » No Vendor Lock-in from proprietary file formats or encryption. ASCII database for transportability and ease of use with other programs and revision control.

- **OpenAccess compliant.**

- » Standard netlist and simulator interfaces.

- » Complete Tcl/Tk programming interface and API.

Micro Magic, Inc. Sunnyvale, CA USA Phone: 408. 414. 7647 www.micromagic.com

Verilog Input DPC works from structural Verilog or Schematics. **Schematic** Generation Creates customlike bit-slice cell **Bit-Slice Placement** placement. **AutoSizer Optimize Design** automatically resizes - Position - AutoSize Gates your gates to improve speed and/or power. 'DPC' It **DPC** estimates Placement routing, times the design, and provides timing feedback. - Route - RC Extract - Timing Info **DPC** computes critical **Critical Path** paths for the design. **Analysis** Design iterations and **Timing** "what-if" analyses are FAST! OK? **DPC** output is a DEF Yes placement file, which is normally sent to your router and combined with other blocks Router

MÍ Micro Magic Inc.

# Faster, Smaller, Lower Power

DPC

# **Use DPC to Make your Datapaths Faster,**

# Typical P&R

2 2

Smaller, Lower Power, **Easy to Route**

- Place, route and time 100K gates per minute.

- Regular bit-slice placement reduces congestion and wire length. reducing size and power.

- Gate Auto-sizer automatically improves timing and power.

- Uses all existing standard cell libraries.

- OpenAccess compliant.

MMI tools greatly increase performance with very little increase in effort.

Using DPC, engineers have produced real

designs that were 3X faster, 40% smaller, and

40% lower power than their existing place &

route design.

Mil Micro Magic Inc.